# Integrated Circuit Analysis Sample Report

# Silicon on Insulator (SOI) Product

#### **IMPORTANT NOTICE**

This report, request for investigation, or analysis is intended to assist our client in product development. This report is copyright protected by LTEC Corporation. Our intention is to provide accurate and reliable information to our customer. While we always aim for maximum precision, an absolute accuracy of all contents in this report cannot be guaranteed.

If contents of this report are used in patent infringement disputes, Ltec cannot accept any liability resulting from potential inaccuracies contained in this report.

Contact in the USA: LTEC Corporation US Representative Office 2280 Zanker Road, No: 203 San Jose CA 95134

Phone: (408) 432-7247 Website: www.ltecusa.com Contact: info@ltecusa.com

Headquarters: LTEC Corporation 42-8, 4-chome, Higashiarioka, Itami-city, Hyogo, Japan

# LTEC Corporation

|                                                          | Page  |              |

|----------------------------------------------------------|-------|--------------|

| 1. Package                                               | 3     |              |

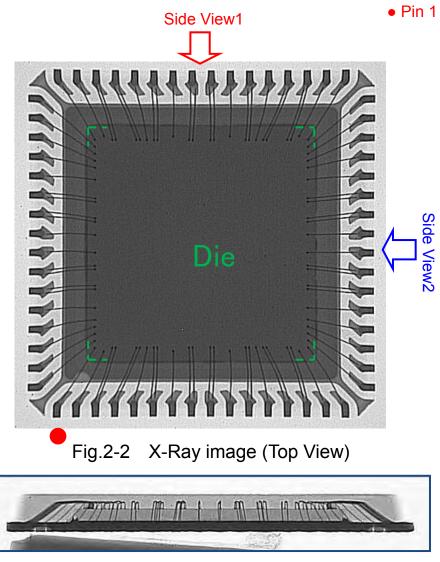

| 2. X-Ray image                                           | 4     |              |

| 3. Die overview                                          | 5-6   |              |

| 4. Cross section analysis                                |       |              |

| 4-0. The location of logic area and Pch/Nch power MOS    | 7     |              |

| 4-1. Logic area cross section                            | 8-12  |              |

| 4-2. Pch power MOS cross section                         | 13-16 |              |

| 4-3. Nch power MOS cross section                         | 17-20 |              |

| 4-4. Layer thickness                                     | 21    |              |

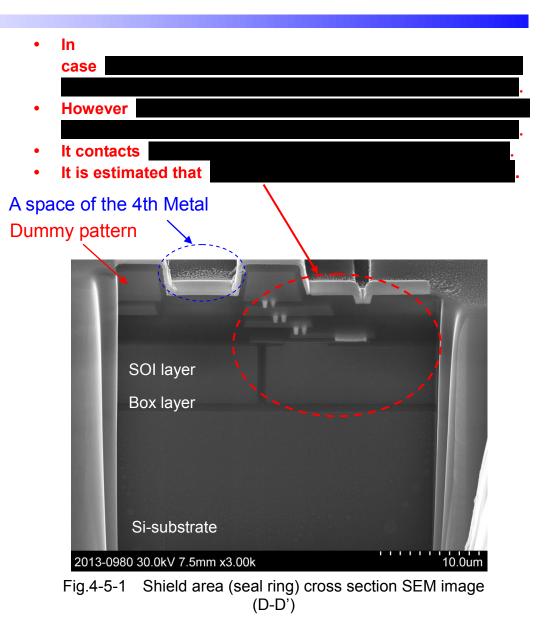

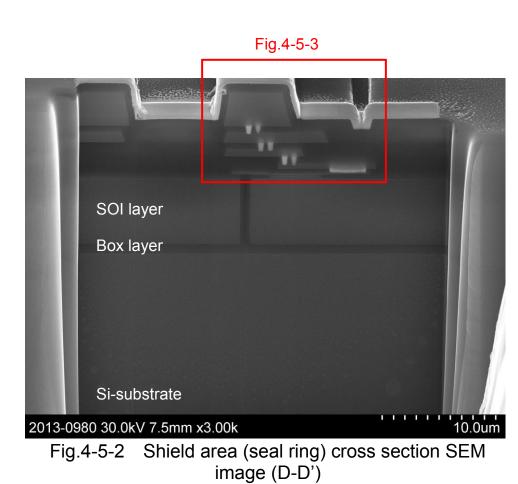

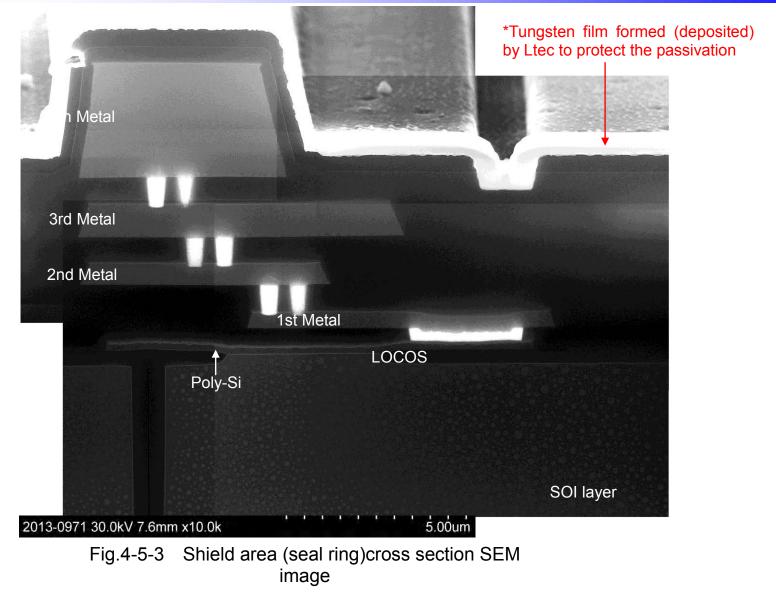

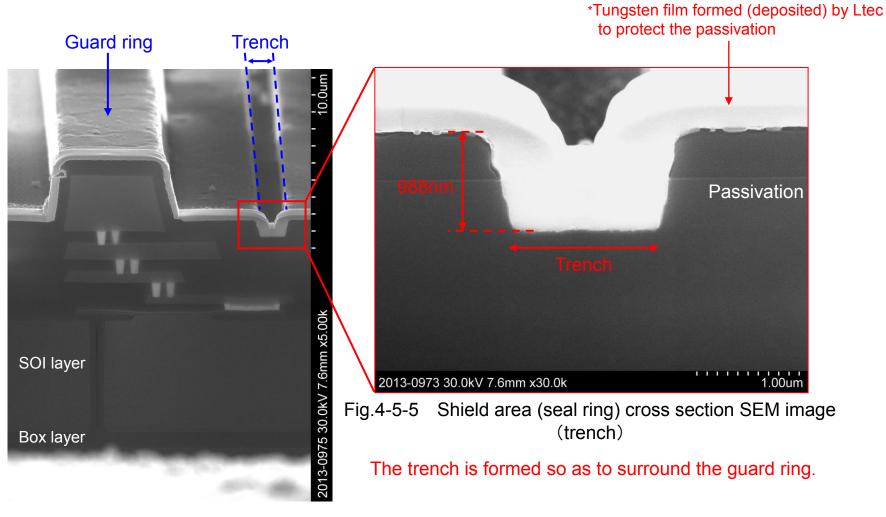

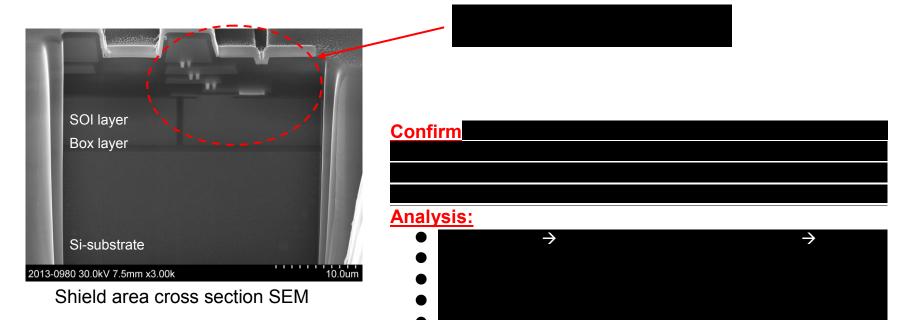

| 4-5. Shield area cross section                           | 22-25 |              |

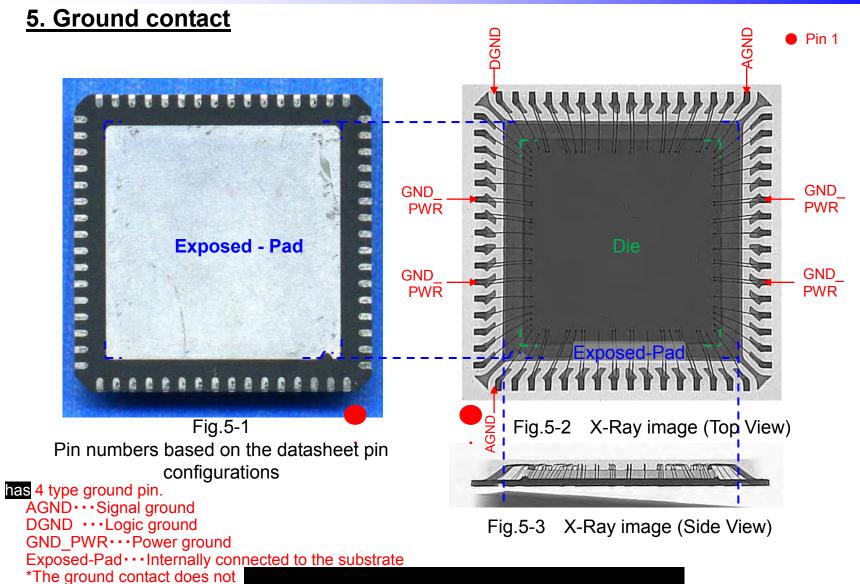

| 5. Ground contact                                        | 26-27 |              |

| 6. Gate oxide thickness in the logic area                | 28    |              |

| 7 Gate oxide thickness in the high-voltage power device, |       |              |

| Recommendation for further analysis                      | 29    |              |

| 8. GND (substrate) contact                               |       |              |

| Recommendation for further analysis                      | 30    |              |

| 9. Patent and literature search                          |       |              |

| Recommendations for further analysis                     | 31    | page:2 of 32 |

| 10. High-voltage SOI products in Japan                   | 32    |              |

|                                                          |       |              |

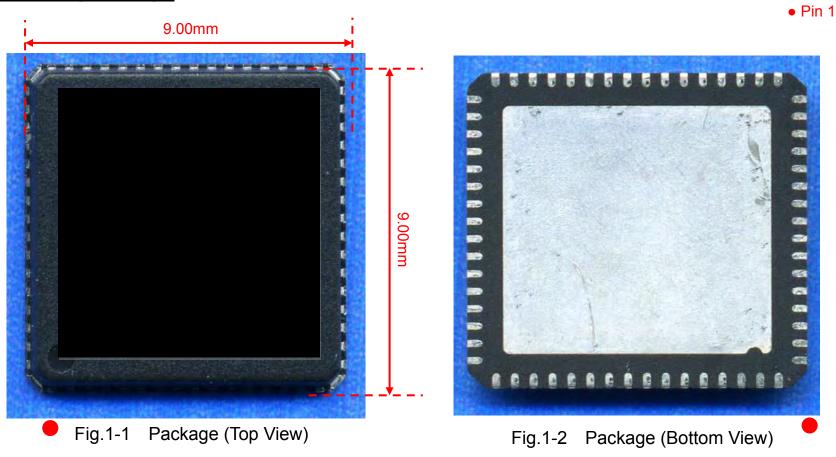

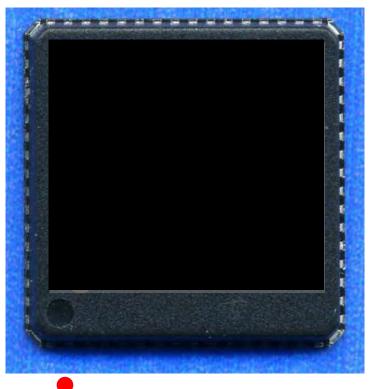

# 1. Package image

Fig.2-1 Package (Top View)

Fig.2-3 X-Ray image (Side View1)

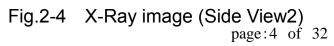

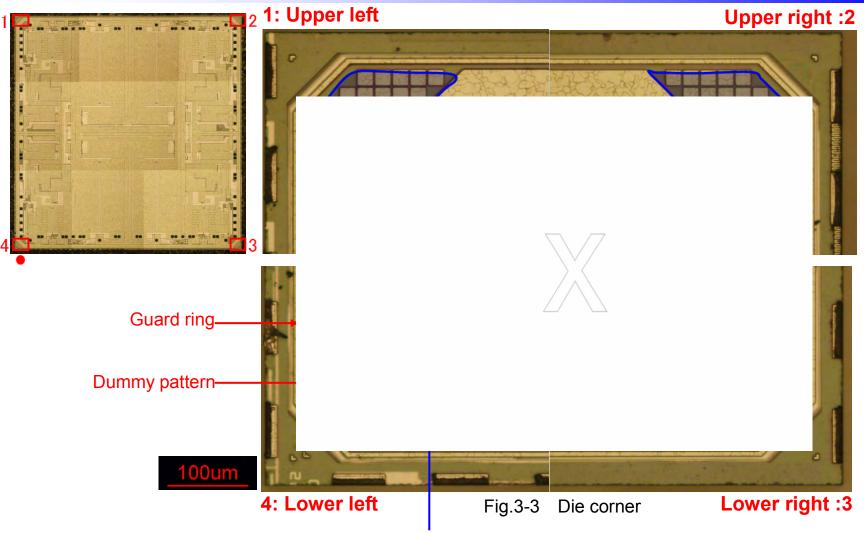

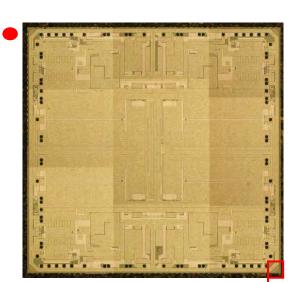

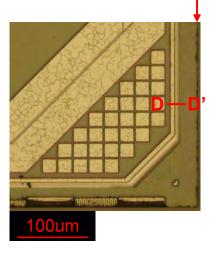

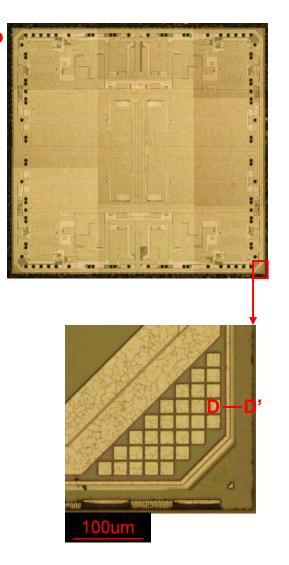

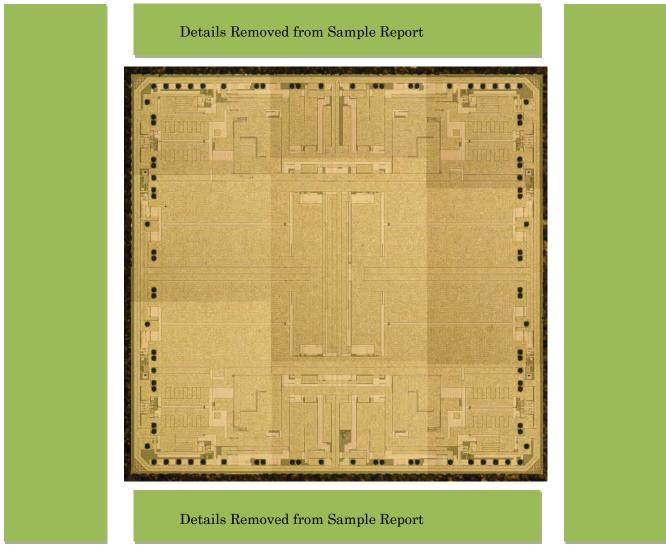

# 3. Die overview

Dummy patterns are placed at the die corners for stress relief.

#### 4. Cross section analysis

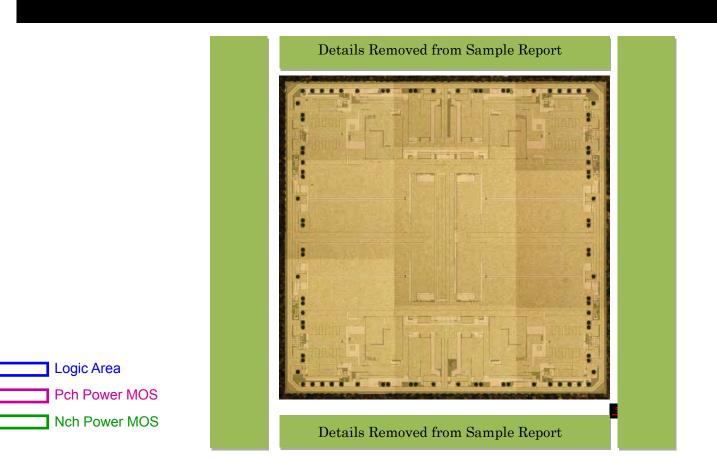

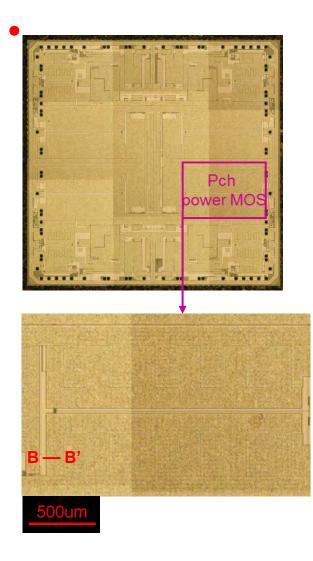

#### 4-0. Logic area and Pch/Nch power MOS locations

Fig.4-0-1 Locations of logic area and Pch/Nch power MOS

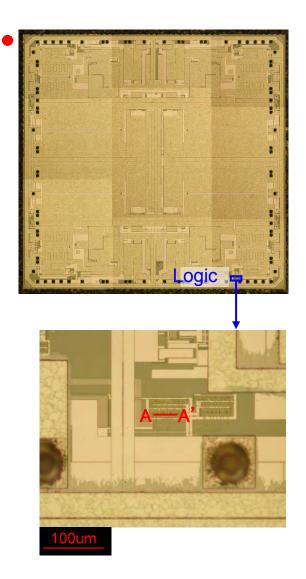

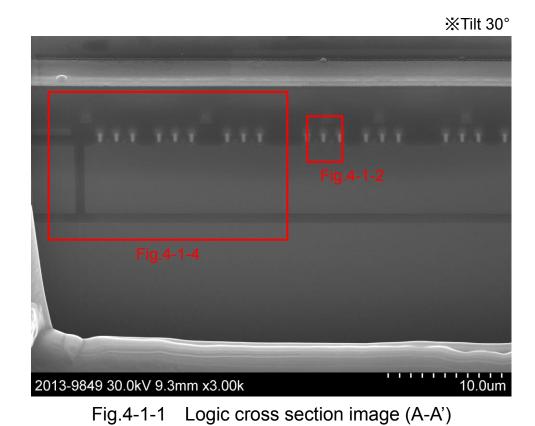

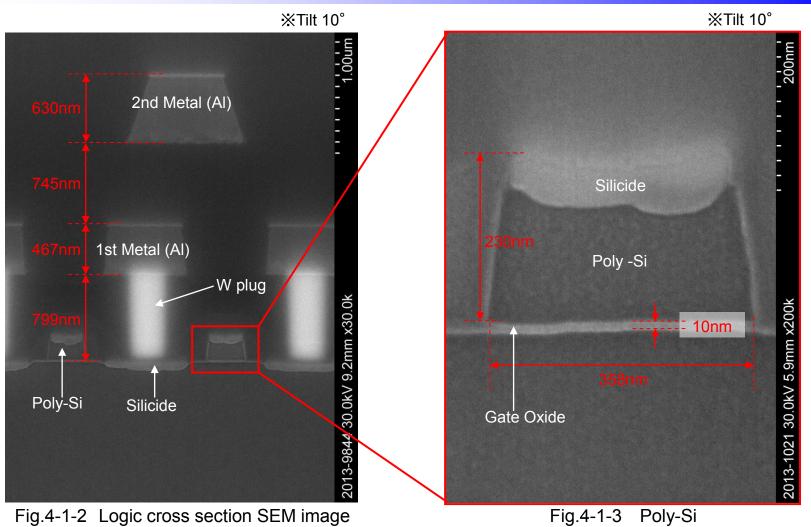

## 4-1. Logic area cross section

• Pin 1

•CMOS process rule of this die is estimated 0.35um process rule.

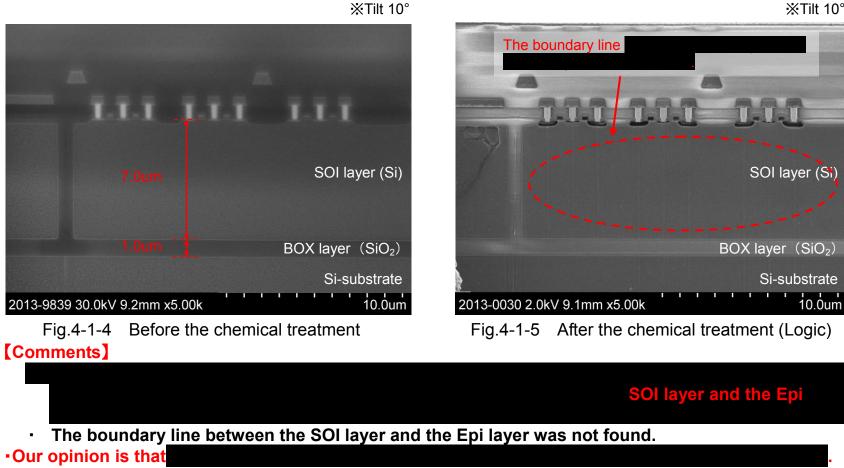

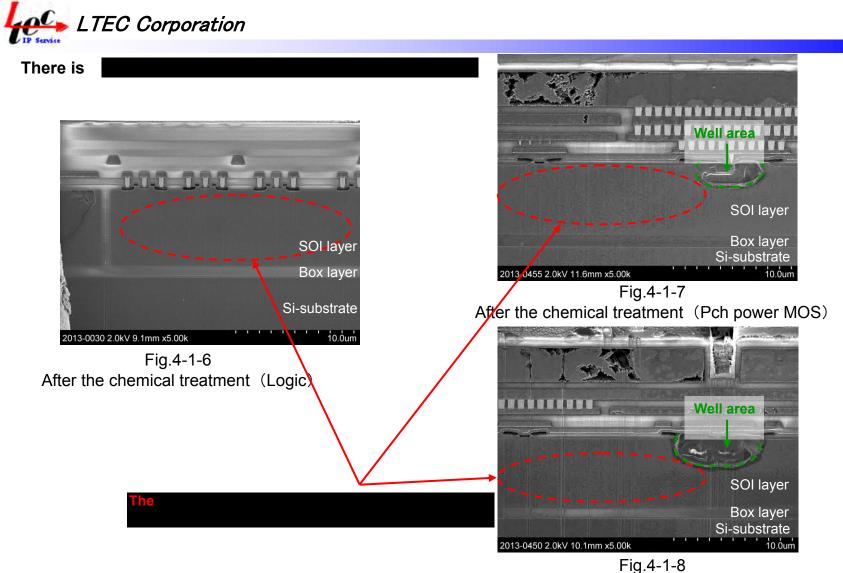

#### LTEC Applied chemical treatment to highlight the Epi layer (if any).

XTilt 10°

After the chemical treatment (Nch power MOS)

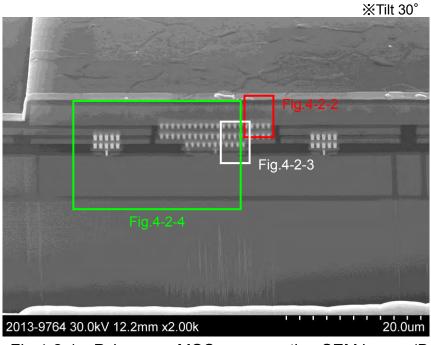

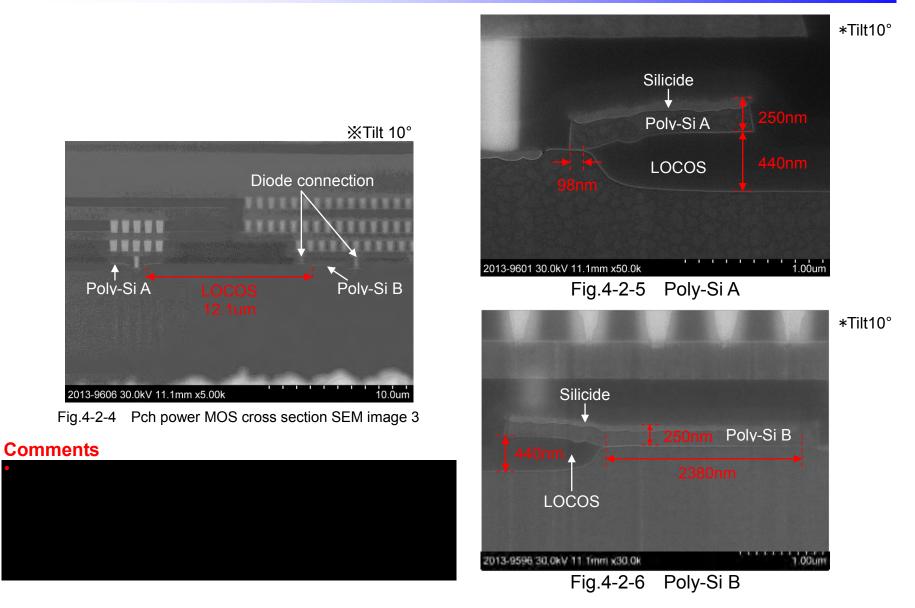

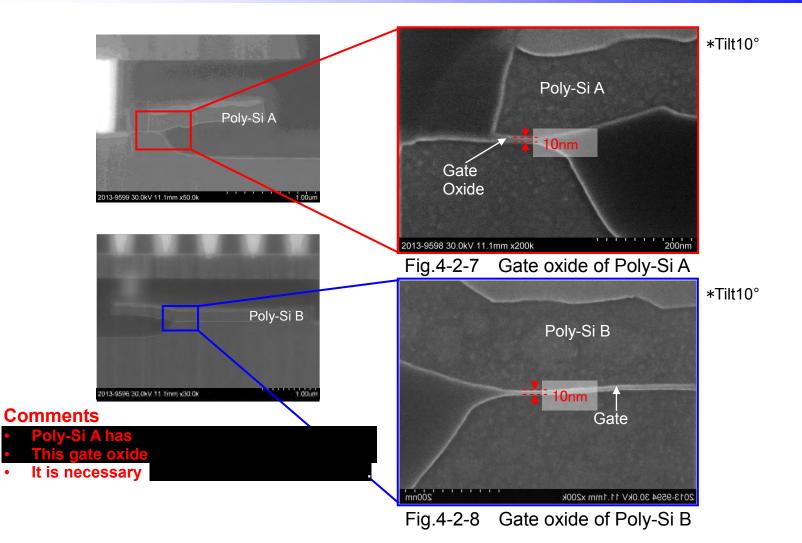

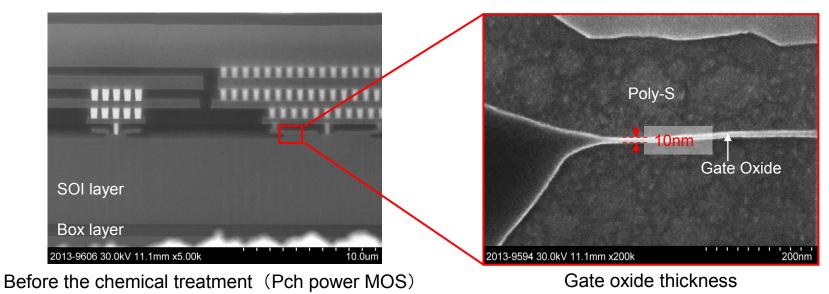

#### 4-2. Pch power MOS cross section

Fig.4-2-1 Pch power MOS cross section SEM image (B-B')

Fig.4-2-2 Pch power MOS cross section SEM image 1

Fig.4-2-3 Pch power MOS cross section SEM image 2

•

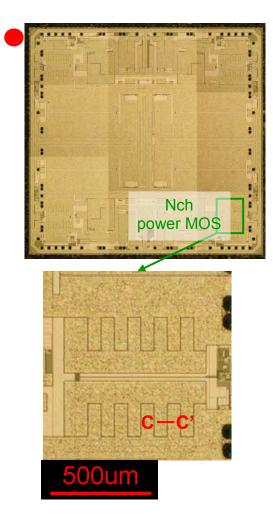

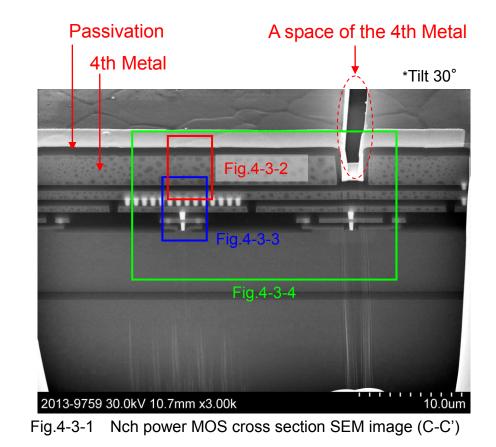

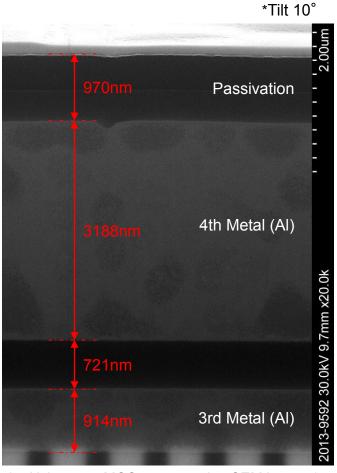

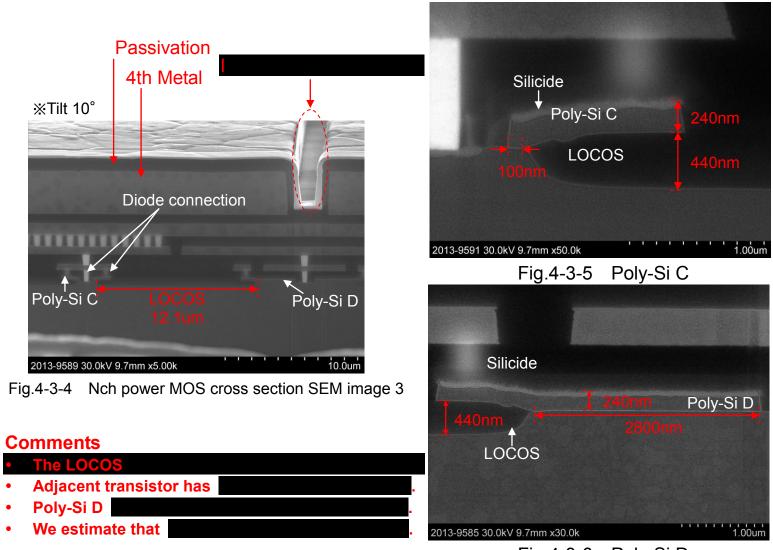

## 4-3. Nch power MOS cross section

• Pin 1

Fig.4-3-3 Nch power MOS cross section SEM image 2

Fig.4-3-2 Nch power MOS cross section SEM image 1

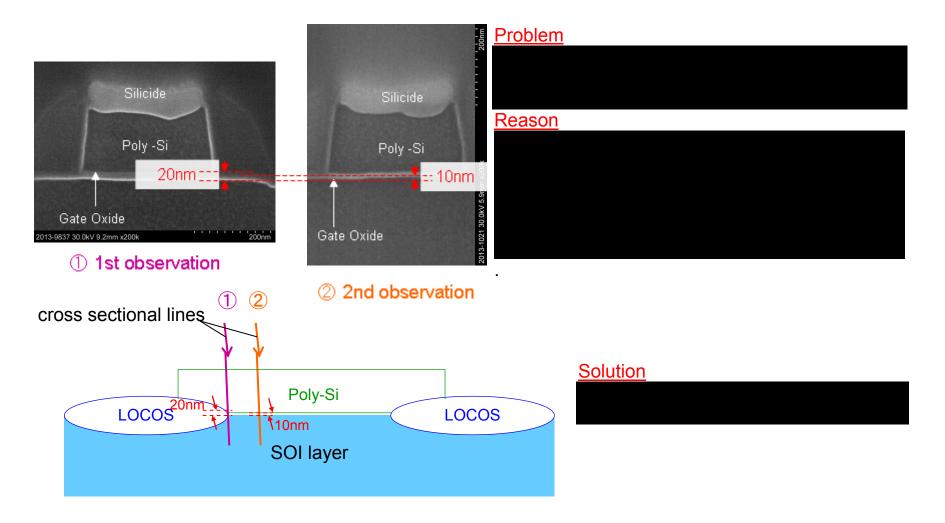

Fig.4-3-6 Poly-Si D

.

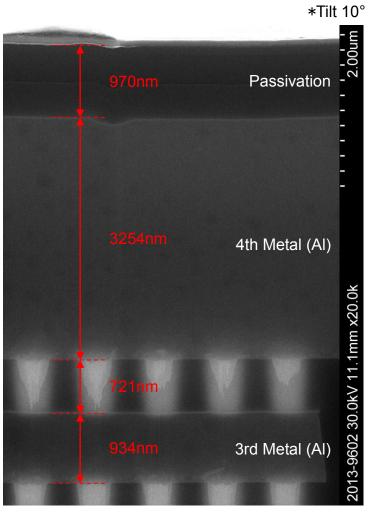

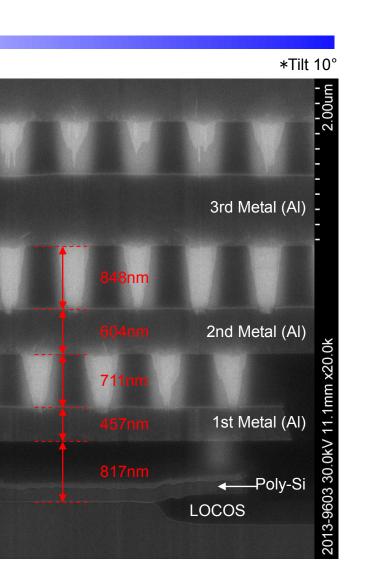

# 4-4. Layer thickness summary

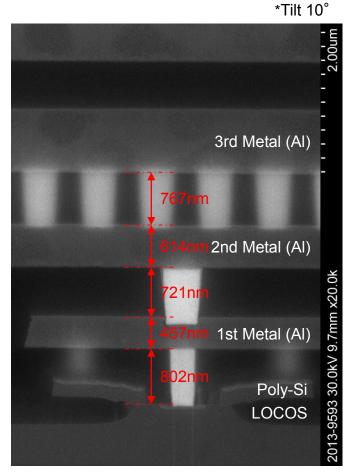

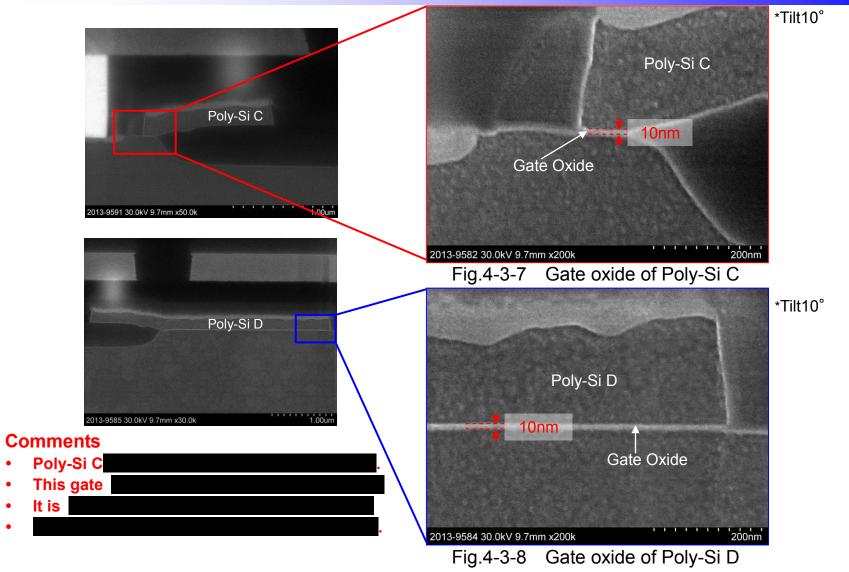

| Measuring point           | Thickness (nm)  |               |               |

|---------------------------|-----------------|---------------|---------------|

|                           | Logic Area (※1) | Pch power MOS | Nch power MOS |

| Passivation               | -               | 970           | 970           |

| 4th Metal                 | -               | 3254          | 3188          |

| 4th Metal - 3rd Metal ILD | -               | 721           | 721           |

| 3rd Metal                 | -               | 934           | 914           |

| 3rd Metal – 2nd Metal ILD | -               | 848           | 767           |

| 2nd Metal                 | 630             | 604           | 614           |

| 2nd Metal – 1st Metal ILD | 745             | 711           | 721           |

| 1st Metal                 | 467             | 457           | 457           |

| 1st Metal – SOI ILD       | 799             | 817           | 802           |

| Gate layer                | 230             | 250           | 240           |

| LOCOS(*2)                 | -               | 440           | 440           |

| Gate Oxide                | 20→10(*2)       | 10            | 10            |

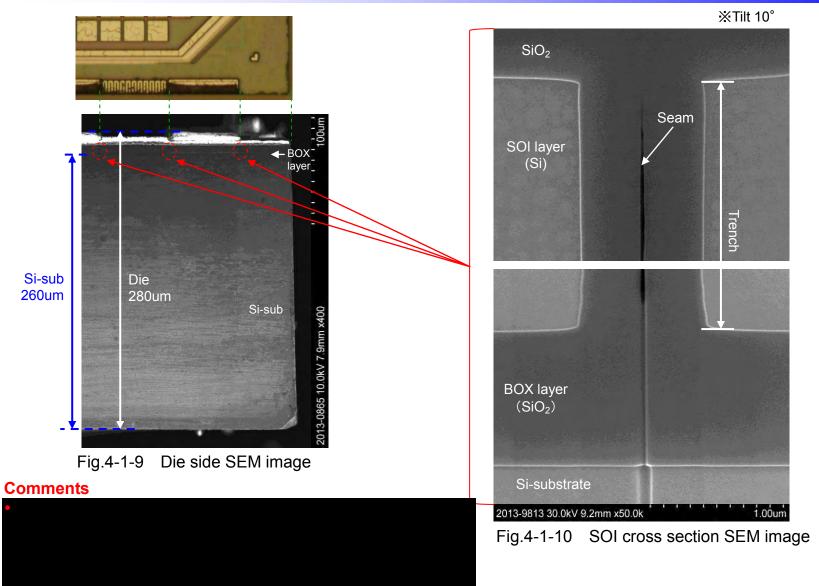

| SOI layer                 | 7000            | -             | -             |

| BOX layer                 | 1000            | -             | -             |

#### Table.4-4-1 layer thickness

\*1 There are no 3rd and 4th Metal in the Logic Area.

\*2 The writing in red identifies corrected or added items.

• Pin 1

page:23 of 32

Fig.4-5-4 Shield area (seal ring) cross section SEM image

FiG.5-4 Pin configurations based on the datasheet

# 6. Gate oxide thickness in the logic area

## Description about the gate oxide thickness in the logic area.

LTEC Corporation

# 7. Gate oxide thickness in the power device Recommendation for further analysis

#### Power device

LTEC has confirmed that

After the chemical treatment (Pch power MOS)

page:29 of 32

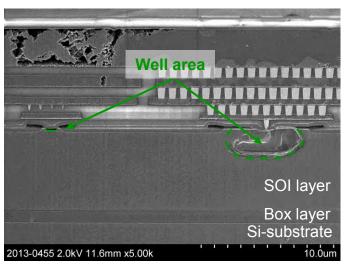

# 8. GND (substrate) contact Recommendation for further analysis

#### Ground contact

# 9. Patent and literature search

Content has been removed from Sample Report

LTEC has identified 497 Japanese patents, 433 has English language version, 64 patents are available in Japanese. All related to high-voltage SOI technology.

Ltec has identified and 82 Japanese publications that relate to high-voltage SOI technology.

In this Excel document we show examples of what was found, identify some key inventor companies and individuals, and make recommendations as to what types of further research could be done.

Pricing associated with individual tasks, has been provided.

# **10. High-voltage SOI products landscape in Japan**

Report on competitive products in JAPAN (To xxxxxxxxx-)